How does 2-ff synchronizer ensure proper synchonization?

Jun 2, 2016 · The are available on RTD. Additional to the theory of chaining 2 flip-flops for a basic 2-FF synchronizer, PoC provides dedicated implementations () for Xilinx and Altera FPGAs to …

fpga - vhdl reset synchronizer - Electrical Engineering Stack …

Nov 15, 2021 · The reset_synchronizer makes sure the reset_sync signal is asserted for at least one rising edge of clk, so no component that uses a synchronous reset will miss it.

How does the second flip-flop in a naive synchronizer "prevent a ...

Jan 13, 2024 · In this very nice answer it's explained that, fundamentally, a two flip-flop synchronizer's basic operation is to prevent the propagation of a metastable state (effectively, …

SDC Constraint for reset synchronizer - Electrical Engineering Stack ...

Apr 6, 2021 · I have a reset bridge in VHDL which is based on a multi-FF synchronizer chain as depicted below. This reset bridge is used in various instances throughout my design. I want to …

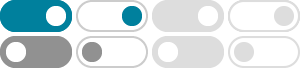

Is it possible to use a 2 flip-flop synchronizer for reset?

Jun 4, 2024 · This delay would obviously break a requirement for the synchronizer output to reset the design immediately on assertion of the reset at the synchronizer input. My question is for …

intel fpga - 2DFF synchronizer output was determined to be a …

Oct 1, 2024 · 2DFF synchronizer output was determined to be a clock by timing analyzer Ask Question Asked 1 year, 2 months ago Modified 1 year, 2 months ago

CDC Synchonisation primitives for an Altera FPGA

Aug 11, 2015 · I updated the synchronizer modules in our PoC-Library and uploaded the first changes to GitHub. Thanks for the link to Altera's attributes.. I'll test it in a Stratix IV design …

Crossing a single-cycle spike signal from a fast clock domain to a ...

Jul 29, 2015 · In extension to the described toggle synchronizer from Alex, this synchronizer offers a busy dignal for the 'write' clock domain. So if busy is high, any input will not be synced …

Asynchronous FIFO design with PULSE synchronizer

Mar 30, 2021 · This design doesn't work because if the reads and writes are high in successive cycles (burst transfer), pulse synchronizer output will only output one pulse in destination clock …

Timing Async Reset with Sync Deassert - Electrical Engineering …

Jul 2, 2022 · For my design, it seems like the best solution is to use asynchronous resets, but with a reset synchronizer circuit to make the de-assert of the reset synchronous. In this scenario, …